innouvs UG描述

endcap cell一般放置在row的两端、最上面和最下面的row形成end-cap ring。围绕在core area、placement blockage和hard macros周围。

为什么加encap cell?

查了资料看到有两种说法:

1.减小PSE(Poly Spacing Effect)和OSE(OD Spacing Effect)的影响;

2.对于多个nwell的设计,因为阱电位可能不一样,要确保每个nwell都是nwell-enclosed,所以在row的end要加endcap(这一点我不是很理解)。

PSE(Poly Spacing Effect)

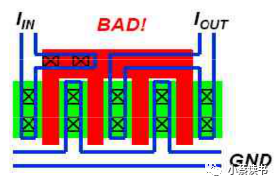

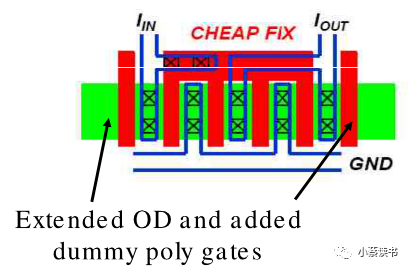

首先来看PSE(Poly Spacing Effect),如下图第一张,由于管子A和管子B周围的环境不一致,在进行光刻、离子注入、刻蚀时,管子A和B的掺杂浓度、受到周围poly的应力等不完全一致,导致管子A和管子B的电学参数不一样。为了保证管子A和管子B的电学参数一致,也就是要保证管子A和管子B的制造环境尽量一致,所以给管子B周围加dummy 管C(一般40nm以下pdk里会自带dummy管)。

PSE:由于Poly的间距原因导致晶体管的性能不一致现象。

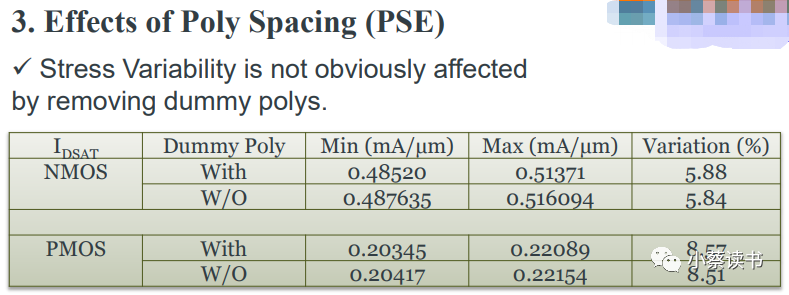

下面所示为28nm PSE对晶体管饱和电流的影响,饱和电流Idsat 是晶体管驱动能力的指标。

OSE(OD Spacing Effect)

如下图所示,第二张比第一张多了额外的OD(绿色区域)和poly(红色部分),多余的poly主要是为了减少PSE的影响,多余的OD就主要是为了减少OSE对器件性能的影响。

OSE:由于OD的应力作用对晶体管电学性能产生的影响。

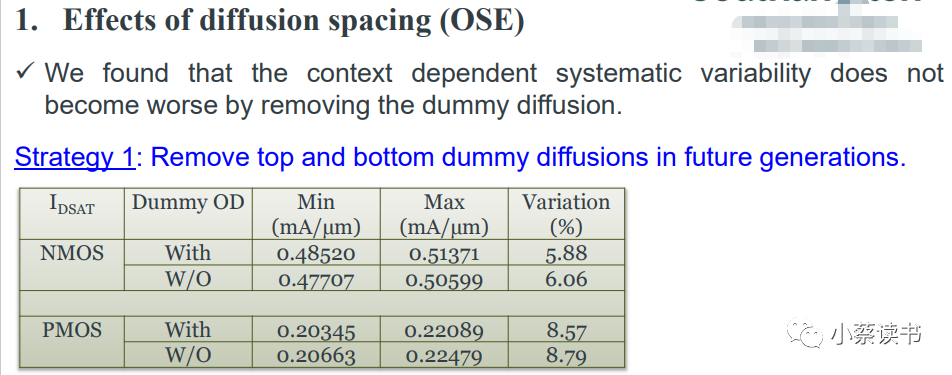

下面所示为28nm OSE对晶体管饱和电流的影响,饱和电流Idsat 是晶体管驱动能力的指标。

总结

由于PSE和OSE对晶体管的电学性能的影响(应力对电学性能的影响下篇介绍),所以需要给晶体管周围加dummy poly和OD,保证一片区域边界晶体管的电学性能和中间晶体管的一致。endcap cell主要就是提供dummy 的poly和OD(是不是可以打开endcap cell 的gds看一看?),这就是需要在开篇提到那些地方加endcap cell的原因。

参考文献:

1.innovus UG

2.《Electrical Variability due to Layout Dependent Effects: Analysis, Quantification, and Mitigation on 40 and 28nm SOC Designs》

3.《Layout-Dependent Proximity Effects》